Cet axe de recherche est né dans les années 90 suite au développement rapide des modules de puissance à IGBT. Ce développement a nécessité de mettre en place des moyens et outils pour une meilleure mise en œuvre des composants semi-conducteurs prenant en compte l’impact des éléments parasites, la gestion thermique et la tenue en tension en particulier. Depuis l’avènement des composants à grand gap en SiC et GaN qui commutent plus vite et ont une surface plus petite, les besoins se sont encore amplifiés.

L’équipe est aujourd’hui impliquée dans différentes études concernant l’impact du module de puissance sur les problématiques de CEM, la tenue en tension et la gestion thermique. Une activité autour du packaging modulaire prenant en compte ces 3 axes est également proposée.

Sont impliqués principalement dans cet axe, Rachelle Hanna, Pierre-Olivier Jeannin, Jean-Luc Schanen et Yvan Avenas, accompagnés de leurs doctorant(e)s, post-doc et stagiaires.

Assemblages de puissance à faible empreinte CEM

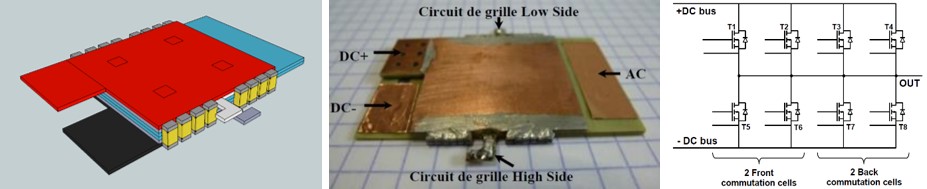

Cette thématique est née dans les années 90 au laboratoire. Elle a d’abord été appliquée sur des modules à base d’IGBT et de MOSFET en silicium. Elle a grandement bénéficié de l’apport du logiciel InCa. Elle a permis d’une part le développement de concepts originaux, tel que le PCoC (Power Chip on Chip) et d’autre part le développement de méthodes d’optimisation pour le placement des composants de puissance dans des modules plus conventionnel (2D). Depuis le milieu de la décennie 2000-2010, l’avènement des composants à grand gap (GaN, SiC et diamant) en électronique de puissance a largement accru les contraintes de design des assemblages de puissance avec pour but d’une part de limiter les surtensions sur les composants de puissance et d’autre part d’avoir des courants de mode communs contenus, tout cela en exploitant les composants à grand gap au maximum de leur vitesse de commutation.

Cela a débouché sur des aspects de packaging originaux afin de réduire les inductances parasites (dans la maille de puissance et dans le circuit de grille) et de maitriser les condensateurs parasites. La maitrise des condensateurs parasites est essentielle pour limiter les courants de mode commun qui sont générés par les forts dv/dt.

Ces travaux ont été menés en collaboration avec des groupes industriels dans le cadre de thèses CIFRE (Thales, Mitsubishi, Alstom, Vedecom) et aussi lors de coopérations académiques lors de projets (ANR, PEPR) ou académiques et industriels (Programme MeGaN, IRT PowerGan).

Ils se poursuivent aujourd’hui par des travaux en cours sur l’utilisation de composants en GaN Verticaux dans le cadre du projet VERTIGO du PEPR Electronique.

Pour mener ces travaux, nous disposons d’une plateforme de mesure CEM et d’une plateforme avec des moyens d’assemblage de composants électronique (CEDMS).

Ci-dessus, l‘exemple d’un module de puissance intégrant dans un circuit imprimé multicouches, huit MOSFETs SiC (puces nues) et des condensateurs de découplages, ce module a été conçu au G2Elab.

Gestion thermique

Les activités autour de la gestion thermique des modules de puissance ont débuté dans les années 90 et ont concerné dans un premier temps le refroidissement monophasique liquide avec des microcanaux. Avec Alstom et le CEA-LETI, le G2Elab a été un précurseur sur les modules de puissance à refroidissement double face. Ensuite, via de nombreuses collaborations, le laboratoire s’est particulièrement intéressé à l’intégration de caloducs miniatures puis à l’utilisation de fluides non conventionnels pour le refroidissement, métaux liquides et ferrofluides en particulier.

Une forte activité a également été menée sur l’utilisation de paramètres thermosensibles pour la caractérisation thermique des modules de puissance. Nous disposons aujourd’hui d’un savoir-faire important dans le domaine qui nous permet de choisir le paramètre thermosensible adapté à l’application visée. Cela nous a par exemple permis de caractériser des attaches de puce thermo-compressées lors du projet ANR CopperPack ou évaluer des solutions de refroidissement intégrant des PCM (Phase Change Materials) dans le cadre du projet NEPTUNE financé par France Relance

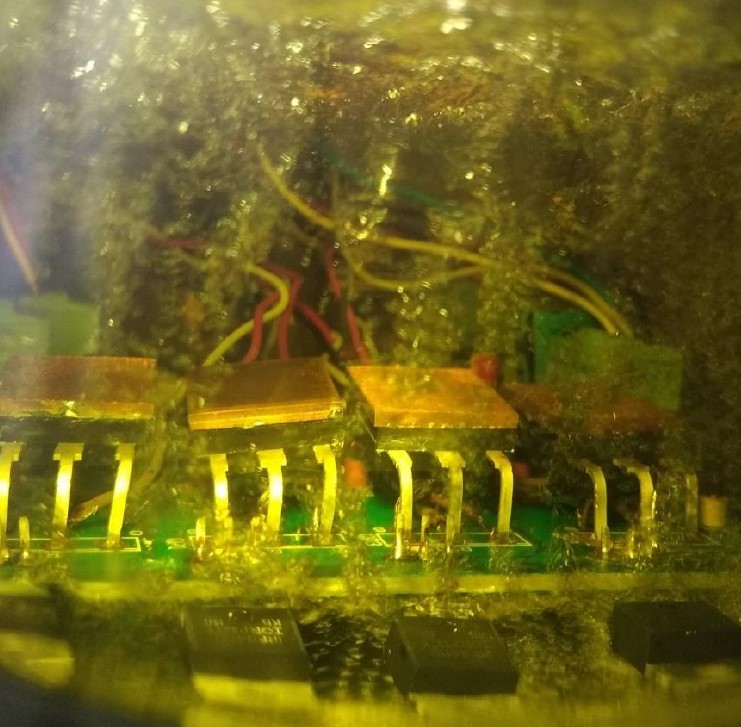

Différents travaux sont en cours sur cette thématique. Dans le cadre d’une thèse CIFRE avec l’entreprise SAFRAN-Tech, nous étudions l’amélioration de la résistance thermique interne au module via l’utilisation de matériaux à forte conductivité thermique. Nous étudions également le refroidissement diphasique par immersion des composants semi-conducteur de puissance en collaboration avec le laboratoire SIMaP (projet MOSAIC de l’Institut Carnot Energies du Futur, projet CDP PowerAlps).

Pour mener ces travaux, nous disposons d’une plateforme incluant plusieurs boucles thermo-hydrauliques et une enceinte instrumentée pour la caractérisation du refroidissement diphasique par immersion. Pour la mesure de température de jonction, nous avons un système de mesure industriel (Phase12B d’Analysis Tech) et des dispositifs « maison ».

Refroidissement diphasique à la surface d'une semelle en cuivre réalisée par impression 3D et brasée sur un transistor en boitier TO220 (vidéo à consulter en affiche plein écran car le format vidéo est vertical)

Refroidissement déphasique à la surface d'une semelle en cuivre lisse soudée sur un transistor en boitier TO220 (video à consulter en affiche plein écran car le format vidéo est vertical)

Packaging modulaire

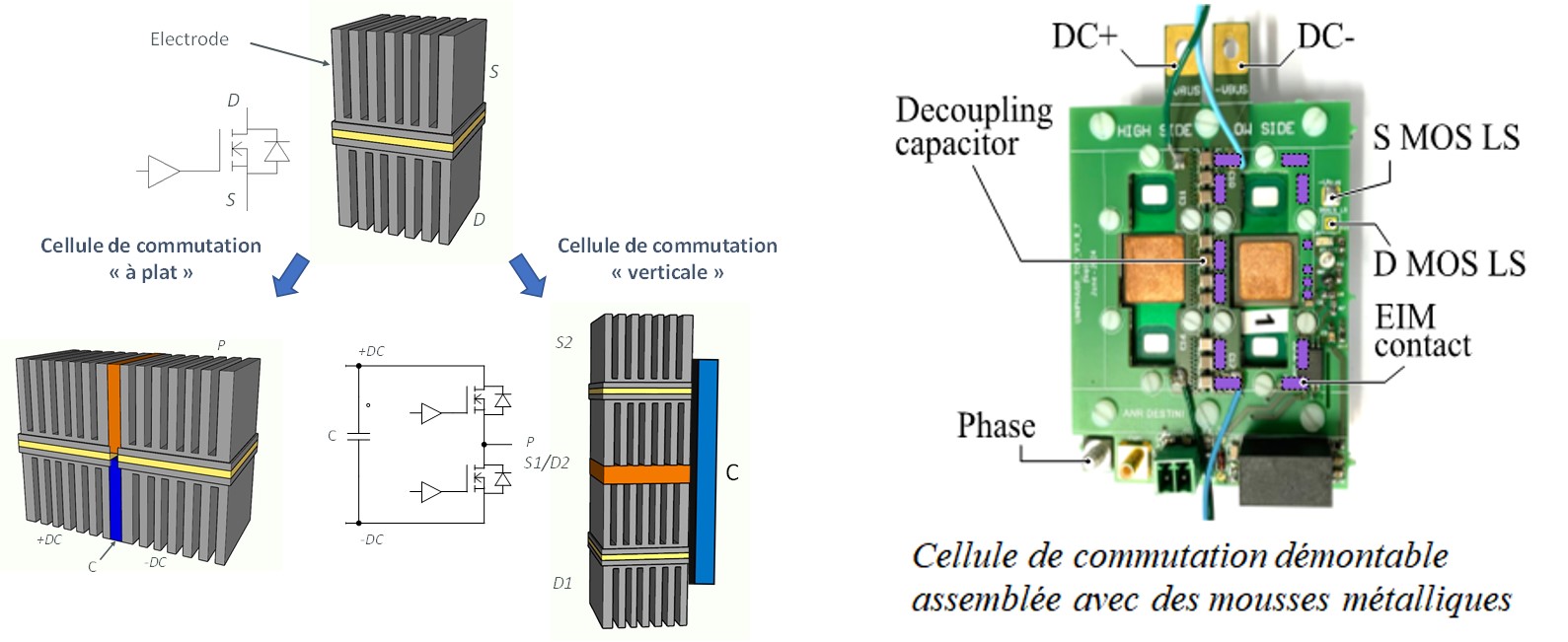

Le packaging modulaire proposé se base sur l’utilisation d’un système élémentaire constitué d’un composant semi-conducteur refroidi sur ses deux faces (voir figure ci-dessous). Cet élément peut être mis en série ou en parallèle avec d’autres éléments pour fabriquer la structure d’un convertisseur. La figure montre par exemple qu’il est possible, à partir de là, de construire une cellule de commutation à faible inductance parasite à condition de disposer d’un condensateur de découplage à proximité. Le concept a été développé lors d’un projet de maturation technologique financé par la SATT Linksium.

Le développement de la modularité permet d’une part de simplifier le design des convertisseurs, mais permet également d’entrevoir la fabrication de modules de puissance plus démontables présentant des performances thermiques intéressantes et des éléments parasites adaptés aux composants rapides. La gestion de la tenue en tension est une problématique importante qui doit être étudiée.

Ainsi, plusieurs projets sont en cours sur ce sujet. Dans une thèse en collaboration avec le CEA, nous étudions la mise en place d’un packaging modulaire et démontable basé sur la mise en œuvre de cellules de commutation verticales. Le refroidissement est effectué par l’utilisation d’un liquide isolant. En parallèle, nous travaillons sur le packaging modulaire et démontable refroidi à air à partir de cellules de commutation à plat dans le cadre des projets TAPIR (Pack Ambition Recherche financé par la région Auvergne-Rhône-Alpes) et DESTINI (ANR, collaboration avec les laboratoires Ampère, SATIE et Laplace).

Publications récentes

- BRUYERE, Paul, VAGNON, Eric, et AVENAS, Yvan. Field Plate Integration for Mitigating Partial Discharge Activity in PCB-Embedded Power Electronic Modules. Energies, 2024, vol. 17, no 9, p. 2035. https://doi.org/10.3390/en17092035

- KHAZAKA, Rabih, HANNA, Rachelle, AVENAS, Yvan, et al. Analysis of Power Modules Including Phase Change Materials in the Top Interconnection of Semiconductor Devices. Electronic Materials, 2024, vol. 5, no 4, p. 204-220. https://doi.org/10.3390/electronicmat5040014

- JANOD, Goulven, CHACHAY, Lucas, SCHOENLEBER, Jonathan, et al. Evaluation of thermocompressed nanoporous copper deposit to replace soldering for power electronic metal foam heat sinks. IEEE Transactions on Components, Packaging and Manufacturing Technology, 2024. https://doi.org/10.1109/TCPMT.2024.3418673

- ALI, Fatme Abed, JEANNIN, Pierre-Olivier, AVENAS, Yvan, et al. Flip-Chip Low inductive and EMC optimized PCB Power Module. In : 2024 IEEE Applied Power Electronics Conference and Exposition (APEC). IEEE, 2024. p. 1534-1538. https://doi.org/10.1109/APEC48139.2024.10509349

- RAMONEDA, Aitor Casado, AVENAS, Yvan, KHAZAKA, Rabih, et al. Thermal and thermo-mechanical behavior of internal silver-diamond heat spreaders for power electronic modules. In : 2024 30th International Workshop on Thermal Investigations of ICs and Systems (THERMINIC). IEEE, 2024. p. 1-6. https://doi.org/10.1109/THERMINIC62015.2024.10732535

- HUGON, Clement, AVENAS, Yvan, FLURY, Sebastien, et al. Test bench for the characterization of two-phase passive immersion cooling of power electronic devices. In : CIPS 2024; 13th International Conference on Integrated Power Electronics Systems. VDE, 2024. p. 325-332.

- FERBER, Moisés, BRUYÈRE, Paul, BOTTER, Nicolas, et al. Stray Inductance of a Modular Switching Cell Designed for Easier Disassembly. In : CIPS 2024. 2024.

- Pawel. B. Derkacz, Jean-Luc. Schanen, Pierre-Olivier. Jeannin, Piotr. J. Chrzan, Piotr. Musznicki and Mickael Petit, "EMI Mitigation of GaN Power Inverter Leg by Local Shielding Techniques," in IEEE Transactions on Power Electronics, vol. 37, no. 10, pp. 11996-12004, Oct. 2022, https://doi.org/10.1109/TPEL.2022.3176943